2011年12月4日 星期日

Do not clear the Intruder Detect bit

SBSECInit.asm

SECSB_EarlyInit PROC PUBLIC

; Disable Auto-Reset Function

mov dx, MKF_TCO_BASE_ADDRESS + TCO_IOREG_CNT1

in ax, dx

out 0edh, al ; I/O delay

or ah, 08t ; Set Bit[11] to disable TCO timer

out dx, ax

out 0edh, al ; I/O delay

mov dx, MKF_TCO_BASE_ADDRESS + TCO_IOREG_STS2

in ax, dx

out 0edh, al ; I/O delay

or al, 02t ; Set Bit[1] to clear SECOND_TO_STS

and al, 0FEh ; Do not clear the Intruder Detect bit ;CN_20110808_JC_02A_01+

out dx, ax

out 0edh, al ; I/O delay

mov esi, MKF_SB_RCRB_BASE_ADDRESS + RCRB_RTC_CONF ; Enable Upper CMOS

mov byte ptr [esi], 04h

mov esi, MKF_SB_RCRB_BASE_ADDRESS + RCRB_MMIO_GCS

mov byte ptr [esi], 60h or (MKF_RESERVED_PAGE_ROUTE shl 2)

2011年7月14日 星期四

2011年7月12日 星期二

Transfer LVDS to HDMI

Intel VGA I.G.D 支援的輸出格式,是以支援標準的輸出格式為主,例如640x480 / 1024x768 / 1280 x 1024…。,。

但是HDMI卻是TV的規格,卻是480i / 720P /1080i /1080p。

所以為了讓PC可以輸出到TV走HDMI,除了硬體的訊號轉換外,還需要修改VGA BIOS。

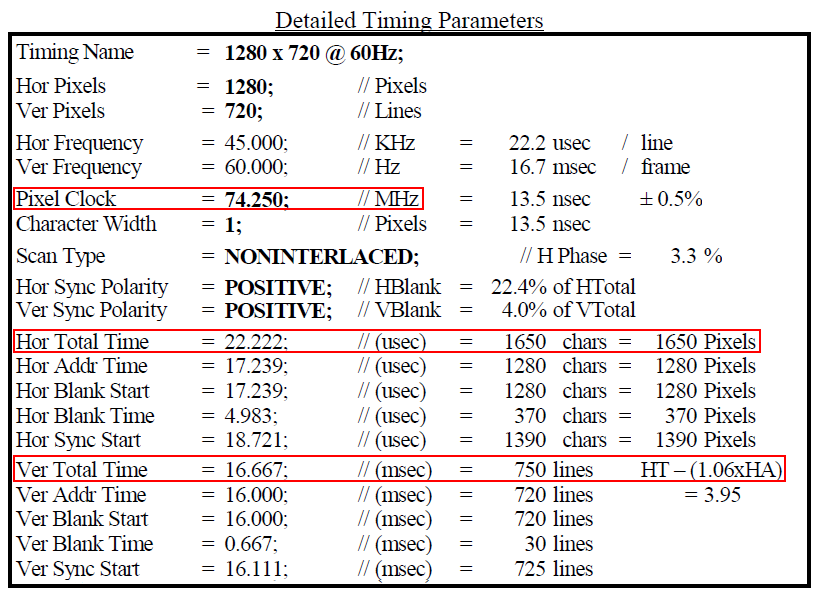

Intel Standard VGA BIOS雖然不支援1280 x 720的解析度,但是VGA BIOS是可以利用BMP修改的,要修改的是LFP Panel的DTD Timings.

而DTD Timings就是依照VESA EDID的規範做的,要填的有18-Byte。

http://en.wikipedia.org/wiki/Extended_display_identification_data

" The table is the 18-byte DTD structure defined in the VESA EDID version 1.x."

DB ? ; Low Byte of DClk in 10 KHz

DB ? ; High Byte of DClk in 10 KHz

DB ? ; Horizontal Active in pixels, LSB

DB ? ; Horizontal Blanking in pixels, LSB

DB ? ; Bit 7-4: Upper 4 bits of Hor. Active

; Bit 3-0: Upper 4 bits of Hor. Blanking

DB ? ; Vertical Active in lines, LSB

DB ? ; Vertical Blanking in lines, LSB

DB ? ; Bit 7-4: Upper 4 bits of Vert. Active

; Bit 3-0: Upper 4 bits of Vert. Blanking

DB ? ; HSync Offset from Hor. Blanking in pix., LSB

DB ? ; HSync Pulse Width in pixels, LSB

DB ? ; Bit 7-4: Lower 4 bits of VSync Offset

; Bit 3-0: Lower 4 bits of VSync Pulse Width

DB ? ; Bit 7-6: Upper 2 bits of HSync Offset

; Bit 5-4: Upper 2 bits of HSync Pulse Width

; Bit 3-2: Upper 2 bits of VSync Offset

; Bit 1-0: Upper 2 bits of VSync Pulse Width

DB ? ; Horizontal Image Size, LSB

DB ? ; Vertical Image Size, LSB

DB ? ; Bit 7-4: Upper 4 bits of Hor. Image Size

; Bit 3-0: Upper 4 bits of Vert. Image Size

DB 0 ; Horizontal Border in pixels

DB 0 ; Vertical Border in lines

DB ? ; Flags:

; Bit 7: 0 = Non-interlaced, 1 = Interlaced

; Bit 6-5: 00 = Reserved

; Bit 4-3: 11 = Digital Separate

; Bit 2: Vertical Polarity (0 = Negative, 1 = Positive)

; Bit 1: Horizontal Polarity (0 = Negative, 1 = Positive)

; Bit 0: 0 = Reserved

=======================================================================================

DB 01h ; Low Byte of DClk in 10 KHz

DB 1dh ; High Byte of DClk in 10 KHz

;Pixel Clock = Horizontal x Vertical x Frame

;Pixel Clock = 1650 x 750 x 60 = 74.25 MHz

DB 00h ; Horizontal Active in pixels, LSB

DB 72h ; Horizontal Blanking in pixels, LSB

DB 51h ; Bit 7-4: Upper 4 bits of Hor. Active

; Bit 3-0: Upper 4 bits of Hor. Blanking

;Horizontal Active -> 1280 = 0500h

;Horizontal Blanking -> 370 = 0172h

DB D0h ; Vertical Active in lines, LSB

DB 1Eh ; Vertical Blanking in lines, LSB

DB 20h ; Bit 7-4: Upper 4 bits of Vert. Active

; Bit 3-0: Upper 4 bits of Vert. Blanking

;Vertical Active -> 720 = 2D0h

;Vertical Blanking -> 30 = 01Eh

2011年7月7日 星期四

GPIO Generate SCI

GPIO_USE_SEL—GPIO Use Select Register

0 = Signal used as native function.

1 = Signal used as a GPIO.

GP_IO_SEL—GPIO Input/Output Select Register

0 = Output. The corresponding GPIO signal is an output.

1 = Input. The corresponding GPIO signal is an input.

GPI_INV—GPIO Signal Invert Register

0 = The corresponding GPI_STS bit is set when the Chipset detects the state of the input pin to be high.

1 = The corresponding GPI_STS bit is set when the Chipset detects the state of the input pin to be low.

GPIO_ROUT—GPIO Routing Control Register (PM—D31:F0)

GPIOxx Route:

00 = No effect.

01 = SMI# (if corresponding ALT_GPI_SMI_EN bit is also set)

10 = SCI (if corresponding GPE0_EN bit is also set)

11 = Reserved

Scope(\_GPE){

Method (_Lxx,0){

Store(0x15, DBG8) // DBG8 name translates to IO port 80h

Sleep (1000) // Wait for 1sec for display DBG8

}

2011年6月19日 星期日

GPIO SETTING

Bit[7:0] = GPIO Number

Bit[8] = 1: GPIO 0:Native

Bit[9] = 1:GPI 0:GPO

Bit[10] = GPIO Level for Input or Output

Bit[11] = Blink

Bit[12] = Signal Invert

訂閱:

意見 (Atom)